因?yàn)閷I(yè)

所以領(lǐng)先

人工智能、AI芯片算力、汽車電子這三個(gè)領(lǐng)域?qū)Ψ庋b技術(shù)的要求各有側(cè)重,因此采用的工藝也有明顯差異。下面我將分別詳細(xì)闡述。

| 領(lǐng)域 | 核心需求 | 關(guān)鍵封裝技術(shù)工藝 |

| 人工智能 (終端側(cè)AI) | 尺寸微型化、功耗低、成本可控 | WLCSP, Fan-In/Out WLP, SiP |

| AI芯片算力 (云端/訓(xùn)練) | 超高算力、極高帶寬、巨大功耗管理 | 2.5D/3D IC (CoWoS, HBM), Chiplets, TCB |

| 汽車電子 | 超高可靠性、耐高溫/振動(dòng)、長(zhǎng)壽命 | QFN, AEC-Q100認(rèn)證的WLCSP/FOWLP, SiP, 功率模塊封裝 |

這個(gè)領(lǐng)域主要指部署在手機(jī)、智能音箱、攝像頭、AR/VR設(shè)備等終端設(shè)備上的AI加速芯片。它們通常用于執(zhí)行輕量級(jí)的推理任務(wù)。

核心挑戰(zhàn):

尺寸限制:設(shè)備內(nèi)部空間極其有限。

功耗限制:需要長(zhǎng)續(xù)航,發(fā)熱必須可控。

成本壓力:面向消費(fèi)電子市場(chǎng),成本敏感。

主要封裝技術(shù):

描述:將處理器、存儲(chǔ)器、無(wú)源元件(電阻、電容)等多個(gè)不同類型的芯片和組件,通過(guò)高密度基板或嵌入式方式集成在一個(gè)封裝體內(nèi),形成一個(gè)功能完整的系統(tǒng)。

優(yōu)勢(shì):極大縮短互連長(zhǎng)度,提升系統(tǒng)性能,減小整體模塊體積。

應(yīng)用:可穿戴設(shè)備、物聯(lián)網(wǎng)模塊中的AI功能集成。

扇入型 (Fan-In):是WLCSP的基礎(chǔ),引腳都在芯片面積內(nèi)。當(dāng)芯片I/O數(shù)量不多時(shí)使用。

扇出型 (Fan-Out WLP):當(dāng)芯片I/O數(shù)量增加,芯片面積內(nèi)無(wú)法容納所有引腳時(shí),將芯片嵌入到環(huán)氧模塑料中,然后在“重構(gòu)的晶圓”上重新分布線路,將引腳“扇出”到芯片實(shí)體面積之外。

優(yōu)勢(shì):在保持小尺寸的同時(shí),實(shí)現(xiàn)了更高的I/O密度和更好的散熱。Fan-Out 技術(shù)非常關(guān)鍵,因?yàn)樗试S集成多個(gè)芯片。

應(yīng)用:蘋果A系列處理器、高通驍龍芯片等廣泛采用。

描述:直接在晶圓上進(jìn)行封裝和植球,完成后切割下來(lái)的芯片尺寸幾乎與裸芯片相同。這是目前最主流的微型化封裝技術(shù)之一。

優(yōu)勢(shì):尺寸極小、電性能好(引線短)、成本低。

應(yīng)用:手機(jī)中的NPU、圖像信號(hào)處理器等。

晶圓級(jí)芯片尺寸封裝 (WLCSP)

扇入型/扇出型晶圓級(jí)封裝 (Fan-In/Fan-Out WLP)

系統(tǒng)級(jí)封裝 (SiP)

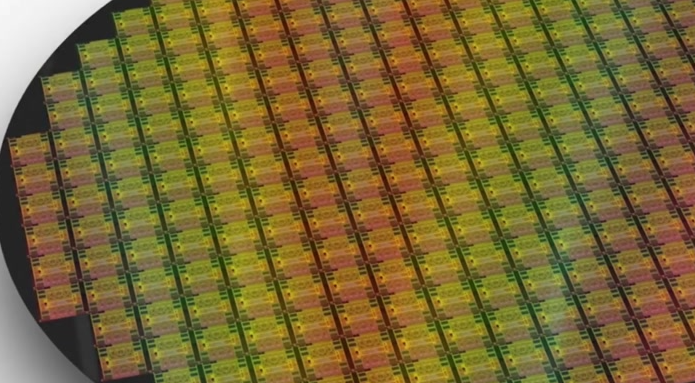

這個(gè)領(lǐng)域指用于數(shù)據(jù)中心、超算等進(jìn)行AI模型訓(xùn)練和大規(guī)模推理的芯片,如NVIDIA的GPU、Google的TPU等。

核心挑戰(zhàn):

性能瓶頸:需要突破“內(nèi)存墻”(內(nèi)存速度跟不上計(jì)算速度)。

互連帶寬:需要極高的芯片間通信帶寬。

熱管理:功耗動(dòng)輒數(shù)百瓦,散熱是巨大挑戰(zhàn)。

主要封裝技術(shù):

描述:一種用于3D堆疊的精密鍵合技術(shù),能實(shí)現(xiàn)更小的凸點(diǎn)間距和更高的連接可靠性,對(duì)散熱也至關(guān)重要。

應(yīng)用:高端3D堆疊封裝的關(guān)鍵工藝。

描述:將一顆大芯片分解成多個(gè)更小、功能更單一的“小芯片”,然后通過(guò)2.5D或3D技術(shù)集成在一起。芯片間采用超高密度互連標(biāo)準(zhǔn),如UCIe。

優(yōu)勢(shì):提升大芯片良率、降低成本、實(shí)現(xiàn)“異構(gòu)集成”(不同工藝節(jié)點(diǎn)的芯片可以組合)。

應(yīng)用:AMD的EPYC處理器是成功案例,AI芯片也廣泛采用此理念。

描述:HBM本身就是3D封裝的典范,它將多個(gè)DRAM芯片堆疊在一起,并通過(guò)TSV與底層的邏輯芯片(GPU)連接。HBM與計(jì)算芯片的集成必須依賴2.5D中介層技術(shù)。

優(yōu)勢(shì):提供遠(yuǎn)超GDDR的帶寬。

描述:這是該領(lǐng)域的核心技術(shù)。

優(yōu)勢(shì):徹底解決了高帶寬內(nèi)存接入問(wèn)題,極大提升了系統(tǒng)性能和能效。

應(yīng)用:所有高端AI訓(xùn)練芯片(NVIDIA H100/GH200, AMD MI300等)都采用2.5D集成HBM。

2.5D:將多個(gè)芯片(如GPU核心和HBM)并排放在一個(gè)硅中介層 上。中介層內(nèi)部有高密度的硅通孔,提供芯片間超高速互連,再通過(guò)中介層下方的焊球連接到PCB上。NVIDIA的CoWoS 是其中最著名的技術(shù)。

3D:將芯片像蓋樓一樣垂直堆疊,通過(guò)硅通孔 直接連接。這提供了最高的互連密度和帶寬。

2.5D/3D 集成封裝

高帶寬內(nèi)存 (HBM) 的集成

Chiplets (小芯片) 與先進(jìn)互連

熱壓鍵合 (TCB)

汽車電子涵蓋范圍很廣,從信息娛樂(lè)系統(tǒng)到最關(guān)鍵的動(dòng)力總成、ADAS(高級(jí)駕駛輔助系統(tǒng))。這里主要討論涉及計(jì)算和功率控制的電子部分。

核心挑戰(zhàn):

極端可靠性:必須保證在-40°C到125°C甚至更高的溫度范圍、高振動(dòng)、高濕度環(huán)境下工作15年以上。

零缺陷要求:尤其是安全相關(guān)部件,故障率要求極低。

大功率處理:電動(dòng)汽車需要處理高電壓、大電流。

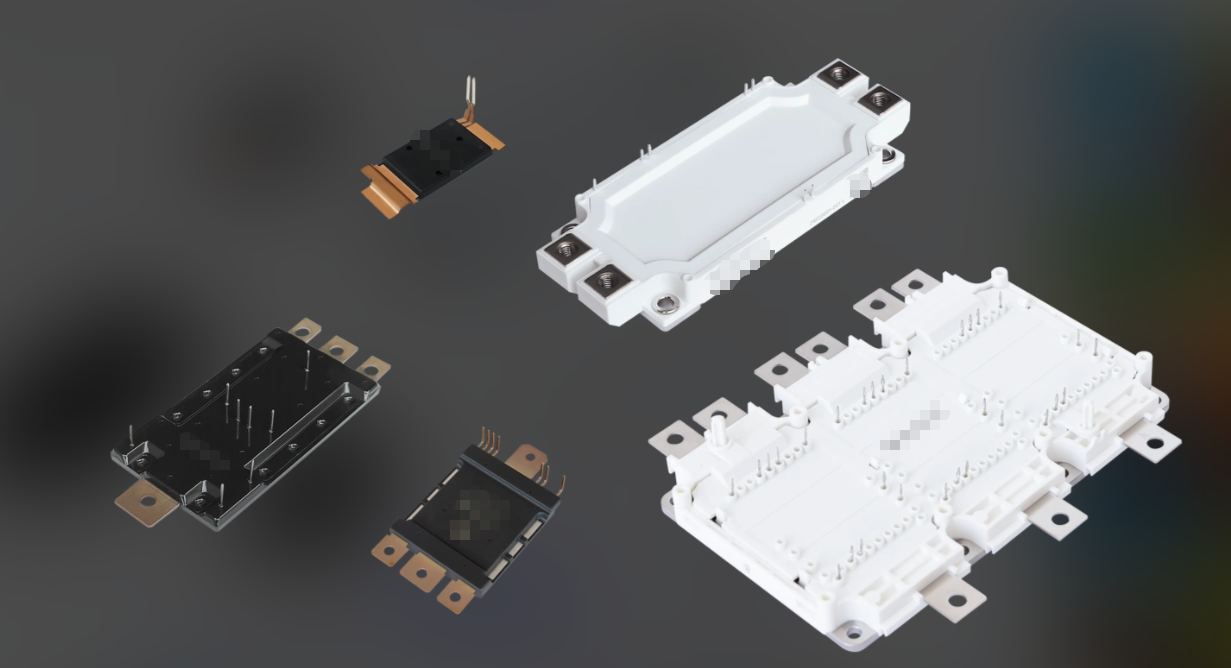

主要封裝技術(shù):

描述:專門用于處理高功率的封裝技術(shù),如電動(dòng)汽車的逆變器中的IGBT和SiC(碳化硅)模塊。

技術(shù):采用直接覆銅基板、銀燒結(jié) 等工藝,確保在高電壓、大電流和高溫下的穩(wěn)定運(yùn)行。

趨勢(shì):從焊接轉(zhuǎn)向燒結(jié),從硅基轉(zhuǎn)向碳化硅/氮化鎵,封裝技術(shù)是關(guān)鍵使能因素。

描述:與消費(fèi)電子類似,但可靠性要求是天壤之別。用于將ADAS域控制器中的多種芯片(如處理器、存儲(chǔ)器、電源管理芯片)集成在一個(gè)高可靠性的封裝內(nèi)。

優(yōu)勢(shì):減少PCB上的元件數(shù)量,提升系統(tǒng)可靠性和抗振動(dòng)能力。

描述:許多封裝形式本身與消費(fèi)電子相同,但必須通過(guò)AEC-Q100等車規(guī)級(jí)可靠性認(rèn)證。這意味著材料、工藝控制和測(cè)試標(biāo)準(zhǔn)都嚴(yán)格得多。

類型:QFN、LQFP 等因其良好的散熱和可靠性,在MCU、傳感器中廣泛應(yīng)用。車規(guī)級(jí)的 WLCSP 和 FOWLP 也用于ADAS攝像頭中的圖像處理器等。

符合車規(guī)認(rèn)證的標(biāo)準(zhǔn)封裝

系統(tǒng)級(jí)封裝 (SiP)

功率模塊封裝

人工智能(終端) 追求 “小而省”,技術(shù)核心是 WLP 和 SiP,在有限空間內(nèi)實(shí)現(xiàn)足夠算力。

AI芯片算力(云端) 追求 “大而快”,技術(shù)核心是 2.5D/3D 和 Chiplets,不惜成本突破性能和帶寬極限。

汽車電子 追求 “穩(wěn)而強(qiáng)”,技術(shù)核心是 車規(guī)級(jí)認(rèn)證 和 高可靠性設(shè)計(jì),在保證萬(wàn)無(wú)一失的前提下,逐步引入先進(jìn)集成和功率封裝技術(shù)。

水基清洗的工藝和設(shè)備配置選擇對(duì)清洗精密器件尤其重要,一旦選定,就會(huì)作為一個(gè)長(zhǎng)期的使用和運(yùn)行方式。水基清洗劑必須滿足清洗、漂洗、干燥的全工藝流程。

污染物有多種,可歸納為離子型和非離子型兩大類。離子型污染物接觸到環(huán)境中的濕氣,通電后發(fā)生電化學(xué)遷移,形成樹枝狀結(jié)構(gòu)體,造成低電阻通路,破壞了電路板功能。非離子型污染物可穿透PC B 的絕緣層,在PCB板表層下生長(zhǎng)枝晶。除了離子型和非離子型污染物,還有粒狀污染物,例如焊料球、焊料槽內(nèi)的浮點(diǎn)、灰塵、塵埃等,這些污染物會(huì)導(dǎo)致焊點(diǎn)質(zhì)量降低、焊接時(shí)焊點(diǎn)拉尖、產(chǎn)生氣孔、短路等等多種不良現(xiàn)象。

這么多污染物,到底哪些才是最備受關(guān)注的呢?助焊劑或錫膏普遍應(yīng)用于回流焊和波峰焊工藝中,它們主要由溶劑、潤(rùn)濕劑、樹脂、緩蝕劑和活化劑等多種成分,焊后必然存在熱改性生成物,這些物質(zhì)在所有污染物中的占據(jù)主導(dǎo),從產(chǎn)品失效情況來(lái)而言,焊后殘余物是影響產(chǎn)品質(zhì)量最主要的影響因素,離子型殘留物易引起電遷移使絕緣電阻下降,松香樹脂殘留物易吸附灰塵或雜質(zhì)引發(fā)接觸電阻增大,嚴(yán)重者導(dǎo)致開路失效,因此焊后必須進(jìn)行嚴(yán)格的清洗,才能保障電路板的質(zhì)量。

合明科技研發(fā)的水基清洗劑配合合適的清洗工藝能為芯片封裝前提供潔凈的界面條件。

合明科技運(yùn)用自身原創(chuàng)的產(chǎn)品技術(shù),滿足芯片封裝工藝制程清洗的高難度技術(shù)要求,打破國(guó)外廠商在行業(yè)中的壟斷地位,為芯片封裝材料全面國(guó)產(chǎn)自主提供強(qiáng)有力的支持。

推薦使用合明科技水基清洗劑產(chǎn)品。

合明科技致力于為SMT電子表面貼裝清洗、功率電子器件清洗及先進(jìn)封裝清洗提供高品質(zhì)、高技術(shù)、高價(jià)值的產(chǎn)品和服務(wù)。合明科技 (13691709838)Unibright 是一家集研發(fā)、生產(chǎn)、銷售為一體的國(guó)家高新技術(shù)、專精特新企業(yè),具有二十多年的水基清洗工藝解決方案服務(wù)經(jīng)驗(yàn),掌握電子制程環(huán)保水基清洗核心技術(shù)。水基技術(shù)產(chǎn)品覆蓋從半導(dǎo)體芯片封測(cè)到 PCBA 組件終端的清洗應(yīng)用。是IPC-CH-65B CN《清洗指導(dǎo)》標(biāo)準(zhǔn)的單位。合明科技全系列產(chǎn)品均為自主研發(fā),具有深厚的技術(shù)開發(fā)能力,擁有五十多項(xiàng)知識(shí)產(chǎn)權(quán)、專利,是國(guó)內(nèi)為數(shù)不多擁有完整的電子制程清洗產(chǎn)品鏈的公司。合明科技致力成為芯片、電子精密清洗劑的領(lǐng)先者。以國(guó)內(nèi)自有品牌,以完善的服務(wù)體系,高效的經(jīng)營(yíng)管理機(jī)制、雄厚的技術(shù)研發(fā)實(shí)力和產(chǎn)品價(jià)格優(yōu)勢(shì),為國(guó)內(nèi)企業(yè)、機(jī)構(gòu)提供更好的技術(shù)服務(wù)和更優(yōu)質(zhì)的產(chǎn)品。合明科技的定位不僅是精湛技術(shù)產(chǎn)品的提供商,另外更具價(jià)值的是能為客戶提供可行的材料、工藝、設(shè)備綜合解決方案,為客戶解決各類高端精密電子、芯片封裝制程清洗中的難題,理順工藝,提高良率,成為客戶可靠的幫手。

合明科技憑借精湛的產(chǎn)品技術(shù)水平受邀成為國(guó)際電子工業(yè)連接協(xié)會(huì)技術(shù)組主席單位,編寫全球首部中文版《清洗指導(dǎo)》IPC標(biāo)準(zhǔn)(標(biāo)準(zhǔn)編號(hào):IPC-CH-65B CN)(“Guidelines for Cleaning of Printed Boards and Assemblies”),IPC標(biāo)準(zhǔn)是全球電子行業(yè)優(yōu)先選用標(biāo)準(zhǔn),是集成電路材料產(chǎn)業(yè)技術(shù)創(chuàng)新聯(lián)盟會(huì)員成員。

主營(yíng)產(chǎn)品包括:集成電路與先進(jìn)封裝清洗材料、電子焊接助焊劑、電子環(huán)保清洗設(shè)備、電子輔料等。

半導(dǎo)體技術(shù)應(yīng)用節(jié)點(diǎn):FlipChip ;2D/2.5D/3D堆疊集成;COB綁定前清洗;晶圓級(jí)封裝;高密度SIP焊后清洗;功率電子清洗。

![[x]](/template/default/picture/closeimgfz1.svg)