因為專業

所以領先

這是一份關于3.5D先進封裝技術,特別是在HPC和AI加速器領域的全面介紹,涵蓋了技術原理、關鍵實現、市場應用和未來趨勢。

在“后摩爾定律”時代,當晶體管微縮的收益遞減、成本劇增時,先進封裝技術成為了延續半導體產業發展的重要引擎。其中,3.5D先進封裝 作為一種關鍵的異構集成技術,通過在高性能計算和人工智能加速器中高效地整合不同工藝節點、不同功能的芯片,實現了系統級性能的飛躍,正成為驅動前沿科技發展的基石。

要理解3.5D,首先需要了解2.5D和3D封裝。

2.5D封裝:

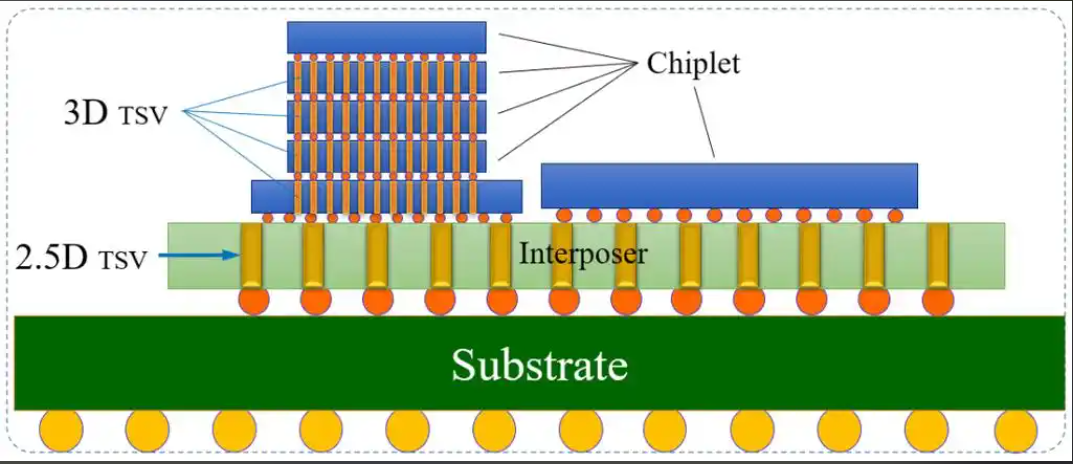

原理:多個芯片(如CPU、GPU、HBM)并排放置在一個硅中介層 上。中介層內部有高密度的硅通孔和布線,充當“超級PCB”,提供芯片間的高速互聯。

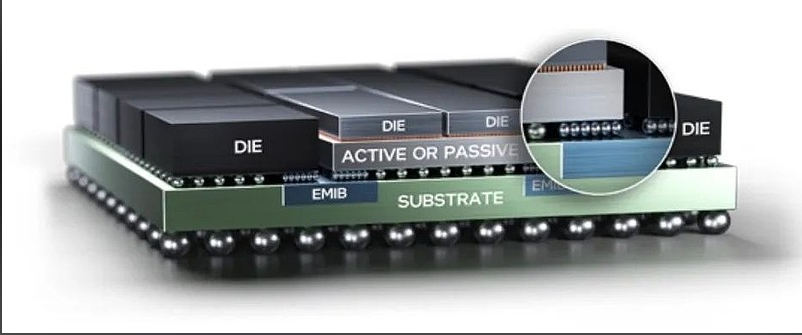

特點:芯片之間通過中介層通信,而不是直接通過PCB,縮短了互聯距離,提高了帶寬和能效。臺積電的CoWoS 和英特爾的EMIB 是典型代表。

3D封裝:

原理:將芯片直接堆疊在另一顆芯片之上,通過硅通孔 進行垂直互聯。

特點:互聯密度最高,延遲最小,但設計和制造復雜度、散熱挑戰也最大。代表技術有臺積電的SoIC。

3.5D封裝 - 一個概念性的定義:

“3.5D”并非一個嚴格的官方術語,而是業界為了描述一種介于2.5D和3D之間、兼具兩者優點的混合集成結構。

核心思想:它不像3D那樣直接堆疊核心計算芯片,而是將多個核心計算芯片(如計算芯粒Chiplets)并排放在硅中介層上(2.5D結構),同時將高帶寬內存等芯片以更緊密的方式(如局部3D堆疊)集成在同一中介層上。

通俗理解:可以看作是在一個強大的2.5D地基上,進行了關鍵部位的3D“加蓋”或“嵌入”,實現了更優的性能、功耗和面積平衡。

在HPC/AI領域,3.5D封裝的核心是實現邏輯芯片(CPU/GPU/ASIC) 與高帶寬內存 的極致集成。

臺積電的CoWoS 是3.5D封裝最典型的實現。其演進歷程清晰地展示了從2.5D到3.5D的路徑:

CoWoS-S:最初的2.5D版本,使用無源硅中介層,在其上放置邏輯芯片和HBM。這是NVIDIA A100、V100等芯片采用的技術。

CoWoS-R:使用RDL(再布線層) 中介層替代硅中介層,成本較低,適用于對互聯密度要求稍低的場景。

CoWoS-L:這就是真正的“3.5D”封裝。

混合鍵合中介層:它結合了局部硅中介層 和LSI(局部硅互聯)芯片。

工作方式:多個計算芯粒并排在中介層上(2.5D結構),而芯粒與芯粒之間的超高速互聯是通過嵌入在中介層中的LSI芯片來實現的。這個LSI芯片就像一個高速交換網絡,提供了比傳統中介層布線更高效、帶寬更高的芯粒間連接。

優勢:實現了比傳統2.5D更高的互聯密度和帶寬,同時避免了整個計算芯片3D堆疊帶來的巨大散熱和設計挑戰。NVIDIA的H100和B200 GPU 就采用了CoWoS-L技術。

硅中介層:是3.5D封裝的“地基”。它由硅制成,可以利用成熟的半導體工藝制作出微米級別的TSV和超高密度布線,其線路密度遠高于傳統PCB。

微凸塊:用于連接芯片與中介層或中介層與封裝基板。其間距越小,互聯密度越高。3.5D封裝要求極小的凸塊間距(例如25μm以下)。

HBM本身也是通過3D堆疊(3D封裝)技術將多個DRAM芯片堆疊在一起。

在3.5D結構中,HBM堆棧通過微凸塊與硅中介層連接,與旁邊的計算GPU/CPU實現超短距離、超高帶寬的通信。這正是滿足AI大模型海量數據吞吐需求的關鍵。

3.5D先進封裝幾乎成為了頂級HPC和AI加速器的“標配”。

NVIDIA:

Hopper架構(H100) 和 Blackwell架構(B200):均采用臺積電CoWoS-L技術。將多個GPU芯粒和HBM3/3E集成在一起,實現了前所未有的芯粒間互聯帶寬(如B200的10TB/s),以支撐萬億參數大模型的訓練和推理。

AMD:

Instinct MI300系列:是異構集成的典范。MI300A將CPU芯粒(Zen 4)、GPU芯粒(CDNA 3)和HBM3全部集成在一個CoWoS平臺上。MI300X則專注于加速計算,集成了多個GPU芯粒和高達192GB的HBM3。這同樣是3.5D集成的典型應用。

Intel:

Ponte Vecchio GPU:采用了英特爾自家的EMIB(2.5D) 和 Foveros(3D) 技術進行混合集成,其復雜結構也符合3.5D的概念。它通過EMIB連接多個計算芯片,并通過Foveros進行3D堆疊,實現了47個芯片單元的異構集成。

云端巨頭自研芯片:

Google的TPU、Amazon AWS的Inferentia和Trainium等雖然具體封裝細節未完全公開,但為了達到頂尖性能,都必然采用了類似的2.5D/3.5D先進封裝技術來集成大量計算核心和HBM。

“內存墻”:傳統架構中,計算單元與內存之間的數據帶寬成為性能瓶頸。3.5D封裝將HBM與計算單元緊鄰放置,極大緩解了此問題。

“功耗墻”:長距離數據傳輸功耗巨大。3.5D的短距離互聯顯著降低了IO功耗,使更多功率可用于實際計算。

“摩爾定律放緩”:單一巨型芯片(Monolithic Die)的制造成本和良率問題突出。3.5D允許使用多個更小、更高良率的“芯粒”來組合成一個大型系統,提升了經濟性。

異構集成需求:AI工作負載需要不同架構的處理器(CPU、GPU、FPGA、專用加速器)和內存協同工作。3.5D提供了理想的異構集成平臺。

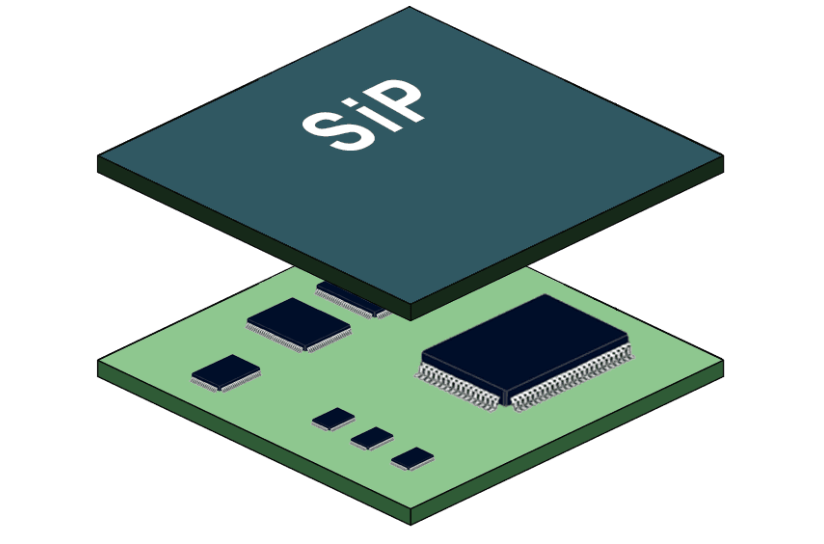

系統性能與小型化:在有限的物理空間內集成更多功能,實現更高的系統級性能。

高昂的成本:硅中介層和先進封裝工藝非常昂貴,是頂級芯片才負擔得起的技術。

設計與測試復雜度:需要芯片、封裝和系統協同設計,帶來了巨大的EDA工具和方法論挑戰。

熱管理:高功率密度芯片集中在一起,產生巨大熱量,需要創新的散熱解決方案(如均熱板、液冷)。

供應鏈與標準:需要建立成熟的芯粒生態和互聯標準(如UCIe),以實現不同廠商芯粒的混搭。

UCIe標準與“Chiplet化”:通用芯粒互聯標準UCIe 的推出,將加速不同廠商芯粒的集成。未來的3.5D封裝可能集成來自臺積電、英特爾、三星甚至第三方IP供應商的芯粒。

光刻技術的結合:隨著CoWoS等中介層尺寸接近光罩極限,未來可能出現“拼接”技術,制造出比光罩尺寸更大的中介層,以支持更龐大的系統。

材料與工藝創新:玻璃中介層、更細的凸塊間距、直接銅-銅混合鍵合等新技術將進一步提升互聯性能和能效。

與3D封裝的融合:未來的系統級封裝可能會看到更多的3.5D基礎結構,并在其上進行核心計算芯片的3D堆疊,形成更復雜的“3D+2.5D”或“3D+3.5D”架構。

3.5D先進封裝已不再是一項可選的技術,而是驅動HPC和AI時代繼續前行的核心使能技術。它通過巧妙的異構集成,成功突破了單芯片的性能、功耗和成本瓶頸,為構建更強大、更高效的計算系統提供了現實路徑。隨著UCIe等生態標準的成熟和制造工藝的進步,3.5D封裝將繼續演進,成為未來算力基礎設施的基石。

水基清洗的工藝和設備配置選擇對清洗精密器件尤其重要,一旦選定,就會作為一個長期的使用和運行方式。水基清洗劑必須滿足清洗、漂洗、干燥的全工藝流程。

污染物有多種,可歸納為離子型和非離子型兩大類。離子型污染物接觸到環境中的濕氣,通電后發生電化學遷移,形成樹枝狀結構體,造成低電阻通路,破壞了電路板功能。非離子型污染物可穿透PC B 的絕緣層,在PCB板表層下生長枝晶。除了離子型和非離子型污染物,還有粒狀污染物,例如焊料球、焊料槽內的浮點、灰塵、塵埃等,這些污染物會導致焊點質量降低、焊接時焊點拉尖、產生氣孔、短路等等多種不良現象。

這么多污染物,到底哪些才是最備受關注的呢?助焊劑或錫膏普遍應用于回流焊和波峰焊工藝中,它們主要由溶劑、潤濕劑、樹脂、緩蝕劑和活化劑等多種成分,焊后必然存在熱改性生成物,這些物質在所有污染物中的占據主導,從產品失效情況來而言,焊后殘余物是影響產品質量最主要的影響因素,離子型殘留物易引起電遷移使絕緣電阻下降,松香樹脂殘留物易吸附灰塵或雜質引發接觸電阻增大,嚴重者導致開路失效,因此焊后必須進行嚴格的清洗,才能保障電路板的質量。

合明科技研發的水基清洗劑配合合適的清洗工藝能為芯片封裝前提供潔凈的界面條件。

合明科技運用自身原創的產品技術,滿足芯片封裝工藝制程清洗的高難度技術要求,打破國外廠商在行業中的壟斷地位,為芯片封裝材料全面國產自主提供強有力的支持。

推薦使用合明科技水基清洗劑產品。

合明科技致力于為SMT電子表面貼裝清洗、功率電子器件清洗及先進封裝清洗提供高品質、高技術、高價值的產品和服務。合明科技 (13691709838)Unibright 是一家集研發、生產、銷售為一體的國家高新技術、專精特新企業,具有二十多年的水基清洗工藝解決方案服務經驗,掌握電子制程環保水基清洗核心技術。水基技術產品覆蓋從半導體芯片封測到 PCBA 組件終端的清洗應用。是IPC-CH-65B CN《清洗指導》標準的單位。合明科技全系列產品均為自主研發,具有深厚的技術開發能力,擁有五十多項知識產權、專利,是國內為數不多擁有完整的電子制程清洗產品鏈的公司。合明科技致力成為芯片、電子精密清洗劑的領先者。以國內自有品牌,以完善的服務體系,高效的經營管理機制、雄厚的技術研發實力和產品價格優勢,為國內企業、機構提供更好的技術服務和更優質的產品。合明科技的定位不僅是精湛技術產品的提供商,另外更具價值的是能為客戶提供可行的材料、工藝、設備綜合解決方案,為客戶解決各類高端精密電子、芯片封裝制程清洗中的難題,理順工藝,提高良率,成為客戶可靠的幫手。

合明科技憑借精湛的產品技術水平受邀成為國際電子工業連接協會技術組主席單位,編寫全球首部中文版《清洗指導》IPC標準(標準編號:IPC-CH-65B CN)(“Guidelines for Cleaning of Printed Boards and Assemblies”),IPC標準是全球電子行業優先選用標準,是集成電路材料產業技術創新聯盟會員成員。

主營產品包括:集成電路與先進封裝清洗材料、電子焊接助焊劑、電子環保清洗設備、電子輔料等。

半導體技術應用節點:FlipChip ;2D/2.5D/3D堆疊集成;COB綁定前清洗;晶圓級封裝;高密度SIP焊后清洗;功率電子清洗。

![[x]](/template/default/picture/closeimgfz1.svg)